Background Material on Data General MV/8000

Data General History / Background

-

"The best small computer in the world," DG Nova brochure,

November 1968, 18 pp. (pdf)

-

deCastro ad (pdf)

-

Simulogics main DG page (with various links)

-

Data General article at wikipedia

-

Data General article at funding universe

-

Data General Nova article at wikipedia

(includes example assembly code)

-

Oral History of Edson de Castro,

Computer History Museum, interviewed by Gardner Hendrie,

November 22, 2002 and January 13, 2003.

- Bill Foster's

memoir of his experience at DG from 1976-1979 as Director

and then VP of Software Development (contains discussion of Eagle

and FHP)

-

Dag Spicer, "The Data General Nova," CHM CORE 2.1 Newsletter,

March 2001, pp. 2-6 (pdf)

- minicomputer timeline - note pressure on minicomputer companies

starting in mid-1970s from microcomputers

- 1950's - MIT Whirlwind, TX-0 and TX-2

- 1960 - DEC PDP-1, first commercial computer equipped with a keyboard

and monitor, 18-bit word size, 28 instructions,

sold for $120,000 in contrast to most other computers

at the time that sold for a million

dollars or more, approximately 50 were built.

(PDP stands for Programmed Data Processor.)

- 1961 - CDC 160A, 12-bit word size, $110,000.

- 1963 - DEC PDP-5, 12-bit word size, $95,000.

- 1965 - CCC DDP-116, 16-bit word size, approximately 200 built, with

several thousand built of follow-on models 516 and 316,

target price was $75,000.

(The designer, Gardner Hendrie, would later go to DG and

design the microNova in 1973-1976.)

- 1965 - DEC PDP-8, 12-bit word size, initially sold for $18,500,

approximately 50,000 built.

- 1967-68 - DEC PDP-X (cancelled), 16-bit word size, designed by

Ed DeCastro and Henry Burkhardt with a register-memory

architecture like the DEC PDP-10

(see

Bob Supnik, "What was the PDP-X?", 2004, pdf)

- 1968 - DG started by former DEC employees

Edson de Castro, Henry Burkhardt, and Richard Sogge, along with

former Fairchild Semiconductor sales manager Herb Richman.

De Castro served as president and CEO;

Richman served as vice-president of marketing and sales;

Harvey Newquist served as head of manufacturing;

and, attorney Frederick Adler served as secretary.

- 1969 - DG Nova, 16-bit word size, typical memory size of 4 K words,

initially sold for $8,000, approximately 50,000 sold across

all the Nova-based product lines. De Castro designed the logic,

Sogge implemented the circuits and memory, and Burkhardt wrote

the software.

- 1970 - DEC PDP-11, 16-bit word size, initially sold for $10,500,

over 600,000 built (perhaps not including LSI-11s?).

- 1970 - DG Supernova SC, Nova instruction set with semiconductor

memory, 3.3 MHz, fastest minicomputer for many years

- 1971 - beginning of microcomputers - Intel 4004.

- 1972 - Intel 8008 microprocessor, 8-bit registers, 16 KB addressability.

- 1973 - Xerox Alto workstation prototype, microcoded processor,

128 KB memory.

- 1974 - DG Eclipse, instruction set extensions to Nova,

microcoded implementation

- 1974 - Intel 8080 microprocessor, 64 KB addressability.

- 1975 - Altair 8800 computer using Intel 8080 and 1 KB memory, $375.

- 1975 - DG starts FHP

- 1976 - Apple I kit, $667

- 1976 - DEC announces plan for VAX superminicomputer

- 1977 - Apple II, $1,300; Commodore PET, $600; Radio Shack TRS-80, $600;

all three come with 4 KB memory.

- 1978 - Intel 8086 microprocessor, 16-bit registers, 1 MB addressability,

$360. (Later 8088 version with 8-bit bus will be used in the

1981 IBM PC.)

- 1978 - top four minicomputer companies are DEC, IBM, DG, and HP.

(IBM was the top computer company overall.)

- 1978 - DEC VAX-11/780, 32-bit word size, typically 256 KB to

2 MB memory size, $120,000 to $250,000+ depending on configuration,

widely sold and by the mid-1980's the VAX product line helped propel

DEC to the number two computer company, behind IBM.

- 1980 - DG MV/8000

(see project timeline below),

$258,000 for medium-scale system with 512 KB main memory, 190 MB disk,

printer, 24 terminals, OS, and compiler

- approximately 100 US minicomputer company attempts from 1965 to 1985

- 1999 - EMC acquires DG, and computer design within the company ends

-

Gordon Bell, "The Coming and Going of Minicomputers:

A DEC Perspective," October 2006 (powerpoint)

Steve Wallach's Designs

- pre-Eagle

- Eagle (MV/8000)

- post-Eagle

-

Convex C-1 - vector minisupercomputer

-

Convey HC-1 - hybrid server using multicore commodity processors

and Xilinx FPGAs

Data General "Eagle" (MV/8000)

- instruction set

- superset of Eclipse C/350 instruction set

- no mode bit (see Michael Meissner's 1987 description of

how compatibility with the Eclipse was achieved)

- about 400 instructions

- four 32-bit integer accumulators

- four 64-bit floating-point registers and one 64-bit FP status register

- four 32-bit wide-stack control registers (stack pointer/base/limit

and frame pointer)

- 16-bit processor status register (3 bits are defined, others are

reserved)

- 31-bit virtual addressability (of 16-bit words), 21-bit physical

addressability

- demand paging, 2 KB pages, 4-byte PTEs with RWX permissions per page

- eight memory segments with memory protection arranged in rings

- AOS/VS assigned levels, four for user and four for OS

- 7 - user program

- 6 - user-defined routines

- 5 - language runtime support

- 4 - (unassigned)

- 3 - extended operating system

- 2 - peripheral manager

- 1 - file system

- 0 - kernel

- transfer to an inner (lower-numbered) ring using xcall or lcall

through specific gate numbers (protected entry points)

- return to outer ring using wrtn

- many instructions had "wide" (32-bit) and "narrow" (16-bit) versions

- several complex instructions were implemented, e.g.,

block move, decimal edit, queue insert/remove along

with 32 different queue search instructions

- MV/8000 Principles of Operation, 1980 (19MB, pdf)

- memory hierarchy

- instruction cache

- 1 KB, direct-mapped

- 64 lines with 16 bytes per line

- three registers used to handle virtual addressing within icache

('399 patent, columns 29 and 30)

- PC - virtual address of instruction being executed

- ICP - icache pointer - virtual address of next instruction

- PICP - physical icache pointer - physical page frame address

corresponding to virtual page addressed by ICP, used to

address the system cache when an icache miss occurs

- a microcode routine for address translation is invoked whenever

a different page is needed for instruction fetch

- system cache

- 16 KB, direct-mapped, unified instruction and data,

physically-addressed, write-back

- 1024 lines with 16 bytes per line (i.e., 8 words per line)

- sits in front of memory and provides dual ports for separate

I/O and CPU accesses, each port capable of providing 32 bits

per 220 nsecs

- a copy of the icache tags are kept in the system cache to

provide for write invalidation of icache lines

- address translation unit (ATU)

- 256-entry TLB (called the ATU address cache)

- reference and modified bits maintained in ATU for each page

of physical memory

- 256-word scratchpad memory in ATU for use by microcode

- main memory

- up to eight 256 KB DRAM modules

- four memory planes within each module,

with planes interleaved on 4-byte boundaries,

16 bytes can be accessed with one address

- 16-byte read take 440 nsecs

- 16-byte write take 550 nsecs

- 4.5 MHz clock frequency versus 5 MHz for VAX-11/780

- microinstruction pipeline (from Epstein, 1980, p. 99)

|<------- 220 ns -------->|<------- 220 ns -------->|

+-------------------------+-------------------------+

| generate address | |

| fetch microinstruction | execute |

| predecode | |

| condition detect | |

+-------------------------+-------------------------+-------

| generate address |

| fetch microinstruction | ...

| predecode |

| condition detect |

+-------------------------+-------

However, Wallach (1981, pp. 113-114) characterizes the machine as

a four-stage, underpipelined design with 110 nsecs cycle time -

(1) fetch instruction, (2) decode, (3) fetch microinstruction, and

(4) execute microinstruction, with the first two stages overlapped

with the last two stages; the Principles of Operations manual

characterizes it as a four-stage, fully pipelined design (1980, p. 15).

Blau, Holland, and Keating (1980, p. 93) also discuss a split-cycle

mode in which the ALU is double-cycled and performs two operations

during a 220 nsecs cycle.

- circuit realizations

- printed circuit boards (PCBs)

- Eagle

- the Blau, Holland and Keating paper says that the Eagle CPU fits

on seven 15" x 15" boards, but the Wallach paper says five boards

(perhaps Wallach is not counting the CC and IOC)

- the ALU fits on one board due to using

AMD 2901 bit slice chips and

PALs (see below)

- initially, the boards were built with

wire wrap

connections (most likely using

IC sockets);

printed circuit boards were used for production

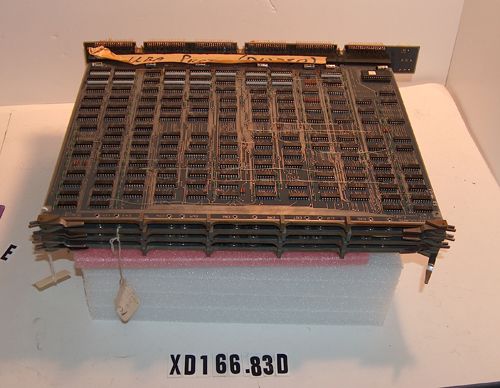

- photo of production IP board

(courtesy Mike Burns, Verdugo Systems & Integration)

-

photo of CPU cabinet with cover removed, showing card cage

(from sets of photos at Australian Computer Museum Society,

Western Australia, of

MV/8000 CPU,

MV/10000 CPU, disk drives, and tape drives)

- comparison with VAX-11/780

- 20-pin PALs (fuse-programmable AND arrays followed by fixed OR arrays)

- each PAL is one-time programmable by electrically blowing fuses

(see

wikipedia entry on PALs)

- 10 inputs, 8 outputs; some outputs can be "registered" (that is,

held in D flip-flops so that they can be fed back into the logic

circuit, see

diagram for 16R4) (see more on PALs and other PLDs in

Ben-Avi, "A Tour of PLDs")

- for an example of use of registered PALs, see Figure 11 (sheet 26,

on page 27 of the pdf) of the '399 patent

- design changes/corrections can sometimes be handled more easily and

quickly by fuse list changes for PALs rather than changing etches on

PCBs (e.g., see section 5 of Blau, Holland, and Keating, 1980, for

a mention of reducing the execution time of lwadd from 4 to 3 cycles

based on PAL changes and no wiring changes)

- 4096 x 75-bit SRAM writeable control store

- 74-bit microinstruction with 1 parity bit (18 fields)

- loaded from diskette by system control processor (a microNOVA

running diagnostics and a console monitor program)

- can be loaded with MV/8000 microprograms or microdiagnostics

- design changes/corrections can sometimes be handled by

distributing modified microcode diskettes

- example input to microcode assembler (one microinstruction per line)

LAB1:F45,T,TRUE,N,S,AC1,GR0,SFIXP,,,,AB,ADD,QREG

CJMP,T,D31,LAB1,,,SATU,,,,,,,,,,,DSN,,RW,R

- basic data path - see Figure 154 (sheet 425, on page 426 of the pdf)

of the '399 patent

- system control processor

- microNova-based diagnostic and console monitor

- power margining stresses components by running

with up to 5% above normal or 10% below normal power

- clock margining can vary clock from 200 nsecs to 240 nsecs

- can deactivate the instruction cache, system cache, and/or

address translation cache

- MV/8000 magazine articles

- MV/8000 technical resources

- Jonathan Blau, Charles Holland, and David Keating,

"The micro-architecture of the ECLIPSE MV/8000: Conception

and implementation" (ACM DL link), MICRO-13, 1980.

- David Epstein,

"The ECLIPSE MV/8000 microsequencer" (ACM DL link),

MICRO-13, 1980.

- Neal Firth,

"The role of software tools in the development of the ECLIPSE

MV/8000 microcode" (ACM DL link), MICRO-13, 1980.

- Paul Reilly, Elizabeth Shanahan, and Steven Staudaher,

"An implementation of microdiagnostics on the ECLIPSE MV/8000"

(ACM DL link), MICRO-13, 1980.

- Steve Wallach and Chuck Holland, "32-bit minicomputer achieves

full 16-bit compatibility," Computer Design, vol. 20, no. 1,

January 1981, pp. 111-120.

- Stephen Worth,

"Benchmarking, Analytic Modelling, and Performance Analysis of

a Data General Eclipse MV/8000," (4 MB, pdf) MS Thesis,

NC State University, 1985.

[Chapter 1 describes the MV/8000 hardware and the AOS/VS operating

system]

-

MV/10000 Microprogrammers' Reference Manual (12 MB, pdf)

- Patents

-

"Data processing system," E. Rasala, S. Wallach, C. Alsing,

K. Holberger, C. Holland, T. West, J. Guyer, R. Coyle, M. Ziegler,

and M. Druke, U.S. Pat. No. 4,386,399, issued May 31, 1983.

(610 pp., 16 MB pdf)

- "Data processing system utilizing a hierarchical memory storage system,"

S. Wallach, K. Holberger, D. Keating and S. Staudaher,

U.S. Pat. No. 4,409,655, issued July 29, 1983.

- "Data processing system having a unique instruction processor system,"

K. Holberger, J. Veres, M. Ziegler and C. Henry,

U.S. Pat. No. 4,398,243, issued Aug. 9, 1983.

- "Arithmetic unit for use in data processing systems,"

J. Blau and J. Rosen,

U.S. Pat. No. 4,405,992, issued Sept. 20, 1983.

- "Hierarchical memory ring protection system using comparisons of

requested and previously accessed addresses,"

S. Wallach, K. Holberger, D. Keating, and S. Staudaher,

U.S. Pat. No. 4,409,655, issued Oct. 11, 1983.

- "Data processing system having instruction responsive apparatus

for both a basic and an extended instruction set,"

C. Holland, S. Wallach and C. Alsing,

U.S. Pat. No. 4,434,459, issued Feb. 28, 1984.

- "Fixed point and floating point computation units using commonly

shared control fields," J. Blau and J. Stein,

U.S. Pat. No. 4,476,537, issued Oct. 9, 1984.

- "Dual port cache with interleaved read accesses during alternate

half-cycles and simultaneous writing," M. Ziegler and M. Druke,

U.S. Pat. No. 4,493,033, issued Jan. 8, 1985.

- "Data processing system having a unique address translation unit,"

S. Wallach, K. Holberger, S. Staudaher, and C. Henry,

U.S. Pat. No. 4,532,590, issued Jul. 30, 1985.

- "Microsequencer in a data processing system using stack storage

for controlling the sequencing of microroutines,"

D. Epstein and C. Holland,

U.S. Pat. No. 4,679,138, issued Jul. 7, 1987.

- ... among others ...

- approximate Eagle project timetable

- July 1975 - FHP project starts

- September 1977 - EGO vs. FHP meeting; FHP version promised in a year

- spring 1978 - Eagle project starts

- summer 1978 - recruiting of Hardy Boys and Microkids

- early 1979 - news that FHP will miss deadline "by a huge margin"

- April 1979 - projected Eagle completion date (missed)

- June 1979 - West presents Eagle at Product Board Meeting

- mid-1979 - Eagle supporter and VP of Engineering Carl Carmen leaves DG

- October 1979 - Gallifrey Eagle moved to software department

- November 1979 - Tom West transferred

- 2H79 and early 1980 - difficulties with PAL supplier;

hardware debugging and software development continue

- April 1980 - public announcement of MV/8000

- fall 1980 - Eclipse group reorganized

- November 1981 - FHP demo

Data General FHP (Fountainhead Project)

Fountainhead Project

Discussion questions for The Soul of a New Machine

Examples of iterative design during the Eagle project